### Hacking the Systems from Within

### André Leitão Nunes da Silva

Thesis to obtain the Master of Science Degree in

### **Electrical and Computer Engineering**

Supervisor(s): Doctor Ricardo Jorge Fernandes Chaves Doctor Aleksandar Ilic

### **Examination Committee**

Chairperson: Doctor Teresa Maria Sá Ferreira Vazão Vasques Supervisor: Doctor Ricardo Jorge Fernandes Chaves Member of the Committee: Doctor Alberto Manuel Ramos da Cunha

January 2021

### Declaration

I declare that this document is an original work of my own authorship and that it fulfills all the requirements of the Code of Conduct and Good Practices of the Universidade de Lisboa.

To my grandparents

#### Acknowledgments

Five years in Técnico, with a one-year break between them, are concluded together with this thesis. It's the end of my cycle towards becoming an engineer; and what a good time it was. Engineering is part of this world both for the good and for the bad, and we need good, creative and ethical engineers to face today's world challenges. I hope this cycle has brought me closer to becoming such one, and I think it did.

There are some people I would like to thank, both for this thesis and for this journey. First of all, I want to thank my supervisors, Ricardo Chaves and Aleksandar Ilíc, for all the attention and help, with the one-hour meetings that quickly became one-and-a-half, with motivation and a smile in everyone's face. It has really been a pleasure working with you.

A big thank you to my mother, for being the engineer of the family, and keeping me inspired and motivated to fight towards all my dreams and goals. Thanks to my father for transmitting me his joy-full and optimistic vibe, and making me see the world in such a way. Thanks to my brothers as well (which, gladly, they will probably never care to read) for being so ambitious and providing such a spirit to our entire family.

I also want to thank my engineer friends, for keeping up for each other and for your rigorous rational and critical thinking, and making the worst tasks and labs a bit funnier; and to my non-engineering friends for reminding me of the most important things of our life.

Finally, a thank you to all the easily-forgotten musicians that bring me joy even when the research results aren't going as expected. Working in silence wouldn't be as fun.

Being thankful is a great feeling. Thank you,

André Nunes da Silva

#### Resumo

A segurança de informação é um factor fundamental para a nossa sociedade tecnológica. Apesar da maioria dos dispositivos utilizarem algoritmos criptográficos matematicamente seguros, estes têm muitas vezes vulnerabilidades na sua implementação física. Os *ataques de canal lateral* permitem comprometer um dispositivo através de informações provenientes da sua concretização física, como o seu consumo de potência, a radiação emitida ou a duração de uma operação. Por outro lado, devido à importância monetária e ambiental do gasto de energia eléctrica, os processadores actuais incluem sensores de consumo de potência, podendo estes ser lidos pelos utilizadores para controlar ou limitar o consumo energético.

O objectivo deste trabalho é analisar a possibilidade e potencial de um ataque de canal lateral utilizando os contadores de energia do processador para obter as chaves de encriptação utilizadas pelo próprio dispositivo. Este método permite a realização de um ataque sem acesso físico ao dispositivo, ao contrário do uso de um osciloscópio para obter os valores de potência utilizado na literatura científica existente. Em contrapartida, a frequência de amostragem é significativamente inferior e obriga a novas adaptações aos ataques habituais.

Para este trabalho de investigação foi feita uma caracterização das medições de energia obtidas num processador Intel, e foi proposto um ataque de modelação posto em prova contra uma versão simplificada do Advanced Encryption Standard. Finalmente, avaliou-se o seu desempenho tendo em conta diversas características do algoritmo. Os resultados indicam que existe uma fuga de informação detectável e capaz de comprometer uma versão simplificada do algoritmo, mas que utilizando o método proposto é insuficiente para obter as chaves de encriptação do algoritmo real. Este trabalho demonstra também que uma análise futura é necessária para avaliar o potencial desta fuga de informação contra outros métodos e algoritmos.

**Palavras-chave:** criptografia, ataques de canal lateral, análise de potência, gestão de energia por software, *running-average power limit*

#### Abstract

Information security is a fundamental aspect of modern technological society. Despite the majority of devices using mathematically secure cryptographic algorithms, it is usual for them to have vulnerabilities in its physical implementation. *Side-Channel Attacks* allow compromising a device using information leaked through its physical properties, such as the power consumption, emanation of radiation or the duration of certain operation. On the other hand, due to the monetary and ecological importance of electric energy spending, modern processors have power consumption sensors included inside, which can be read to monitor or limit the energy consumption.

The goal of this thesis is to analyse the possibility and threat of a side-channel attack using the processors' own energy counters to obtain encryption keys used by that device. This method opens the door to an attack without physical access to the device, in contrary to the usage of an oscilloscope described in current scientific literature. In contrast, the sampling frequency is significantly lower and imposes new challenges to adapt to the current attacking methods.

For this research work, a characterisation of the energy measuring capabilities of an Intel processor was performed and a modulation attack was carried out against a simplified version of the Advanced Encryption Standard. Finally, the performance of the proposed solution was measured under several characteristics of the algorithm. Results show that leakage exists that is detectable and allows compromising the simplified version of the algorithm, but is not enough to obtain the encryption keys of the real version using the proposed method. This work also shows that a future analysis is required to evaluate the threat of this leakage source towards improved methods and algorithms.

**Keywords:** cryptography, side-channel attacks, power analysis, energy-management software, running-average power limit

# Contents

|   | Ackr  | nowledg  | gments                                      | v   |

|---|-------|----------|---------------------------------------------|-----|

|   | Res   | umo .    | · · · · · · · · · · · · · · · · · · ·       | /ii |

|   | Abst  | tract .  |                                             | ix  |

|   | List  | of Table | es                                          | iii |

|   | List  | of Figu  | res                                         | v   |

|   | Acro  | onyms    |                                             | /ii |

| 1 | Intro | oductio  | on                                          | 1   |

|   | 1.1   | Objec    | tives                                       | 2   |

|   | 1.2   | Main (   | Contributions                               | 2   |

|   | 1.3   | Thesis   | s Outline                                   | 2   |

| 2 | Bac   | kgrour   | nd                                          | 5   |

|   | 2.1   | Crypto   | ography                                     | 5   |

|   |       | 2.1.1    | Symmetric Cryptography                      | 5   |

|   |       | 2.1.2    | Asymmetric Cryptography                     | 6   |

|   |       | 2.1.3    | Advanced Encryption Standard (AES)          | 7   |

|   |       | 2.1.4    | Cryptanalysis                               | 8   |

|   |       | 2.1.5    | Side-Channel Attacks                        | 9   |

|   | 2.2   | Comp     | utational Architecture                      | 0   |

|   |       | 2.2.1    | Instruction Set                             | 1   |

|   |       | 2.2.2    | Workflow of a Core                          | 2   |

|   |       | 2.2.3    | Energy Consumption                          | 5   |

|   |       | 2.2.4    | Software-based Energy Measuring             | 6   |

| 3 | Stat  | e of th  | e Art 1                                     | 9   |

|   | 3.1   | Power    | Analysis                                    | 9   |

|   |       | 3.1.1    | Simple Power Analysis                       | 20  |

|   |       | 3.1.2    | Differential Power Analysis                 | 20  |

|   |       | 3.1.3    | Correlative Power Analysis                  | 22  |

|   |       | 3.1.4    | Template Attacks                            | 22  |

|   |       | 3.1.5    | Countermeasures and Counter-countermeasures | 25  |

|    | 3.2        | Attacks based on energy measurement acquired by software | 26       |

|----|------------|----------------------------------------------------------|----------|

| 4  | Pro        | posed Method                                             | 29       |

|    | 4.1        | Interface Characterization of Measures                   | 30       |

|    | 4.2        | Sampling Method and Leakage Detection                    | 31       |

|    | 4.3        | Quantification of Leakage                                | 32       |

|    | 4.4        | Summary                                                  | 32       |

| 5  | lleir      | ng RAPL for sampling Power Consumption                   | 33       |

| Ŭ  | 5.1        |                                                          | 33       |

|    | 5.2        | Sampling Rate                                            |          |

|    | 5.3        | Influence of the Clock on the Sampling Frequency         | 34<br>36 |

|    | 5.3<br>5.4 |                                                          |          |

|    | ••••       |                                                          |          |

|    | 5.5        | Summary                                                  | 39       |

| 6  | Lea        | kage Identification and Processing of Energy Samples     | 41       |

|    | 6.1        | Simplified AES                                           | 41       |

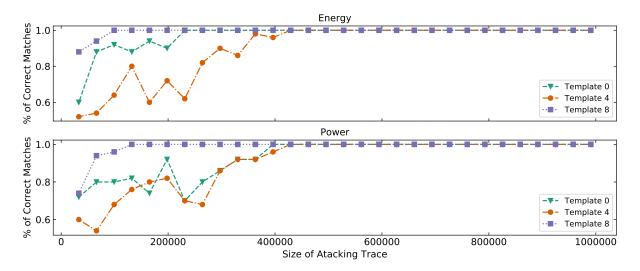

|    | 6.2        | Template Matching and Differentiating                    | 44       |

|    | 6.3        | Power vs Energy                                          | 47       |

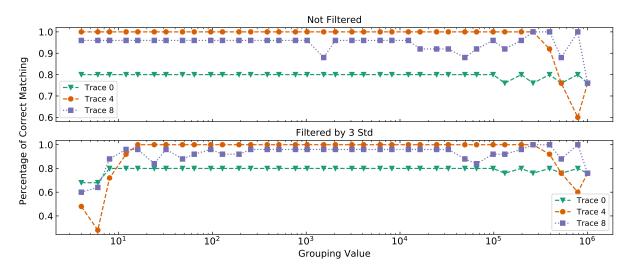

|    | 6.4        | Outliers and Sampling Grouping                           | 48       |

|    | 6.5        | Other Conditions                                         | 50       |

|    | 6.6        | Summary                                                  | 53       |

| 7  | Eva        | luation of Attacks and Potential Threat                  | 55       |

|    | 7.1        | Definition of Attacks                                    | 55       |

|    | 7.2        | Increasing Difficulty                                    | 58       |

|    |            | 7.2.1 Adding Possible Hamming Weights                    | 58       |

|    |            | 7.2.2 Adding Different Bytes                             | 59       |

|    |            | 7.2.3 Increasing Number of Rounds                        | 60       |

|    | 7.3        | Summary                                                  | 61       |

| 8  | Con        | clusions and Future Work                                 | 63       |

| 5  | 001        |                                                          | 00       |

| Bi | bliog      | raphy                                                    | 67       |

# **List of Tables**

| 2.1 | Examples of x86 Instructions                          | 12 |

|-----|-------------------------------------------------------|----|

| 2.2 | x86 Instructions Types                                | 12 |

| 2.3 | Scheduler Ports and Execution Units                   | 15 |

| 6.1 | T-Test and Confusion Matrixes                         | 46 |

| 6.2 | Influence of other processes in acquisitions          | 51 |

| 6.3 | Performance of classification on another architecture | 53 |

| 7.1 | Confusion matrix with 5 different Hamming eights      | 58 |

| 7.2 | Confusion matrix with all Hamming Weights             | 58 |

| 7.3 | Confusion Matrices for Random Bytes                   | 60 |

# **List of Figures**

| 2.1  | Symetric Cryptography                                | 6  |

|------|------------------------------------------------------|----|

| 2.2  | Asymmetric Cryptography                              | 6  |

| 2.3  | Advanced Encryption Standard Overview - Encryption   | 7  |

| 2.4  | Advanced Encryption Standard Overview - Decryption   | 8  |

| 2.5  | Black-Box Model                                      | 9  |

| 2.6  | Grey-Box Model                                       | 9  |

| 2.7  | Skylake's Chip Diagram                               | 11 |

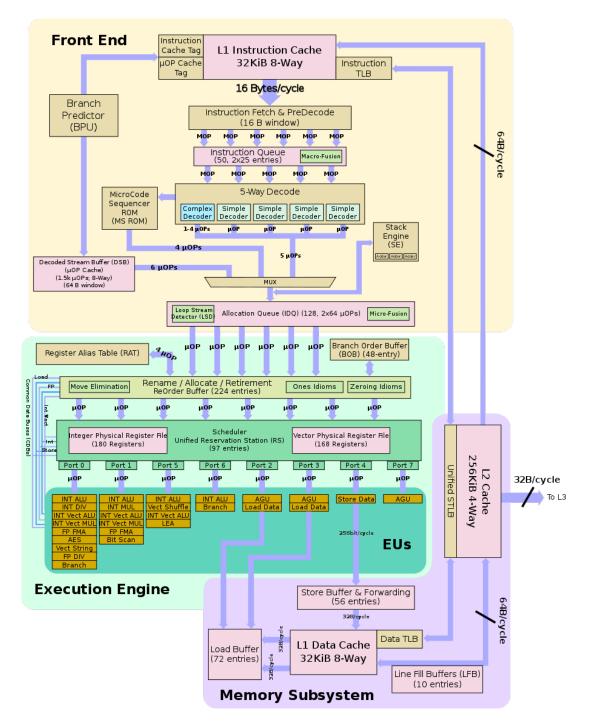

| 2.8  | Diagram of a Processor's Core                        | 13 |

| 2.9  | CMOS Inverter Gate                                   | 16 |

| 2.10 | Quantization of a Signal                             | 18 |

| 3.1  | Power Trace of a DES encryption using a Smart-Card   | 19 |

| 3.2  | Detail of a DES Encryption Power Trace               | 20 |

| 3.3  | Selection Function designed for AES                  | 21 |

| 4.1  | Conceptual Architecture                              | 30 |

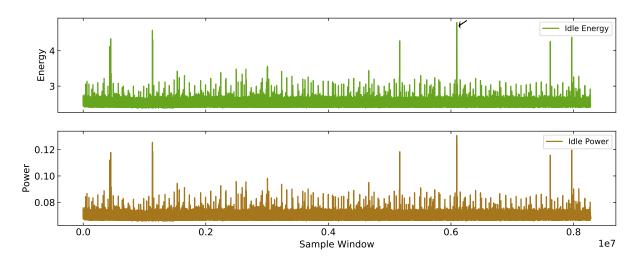

| 5.1  | Sampling Rate and Reading Frequency Acquisition      | 34 |

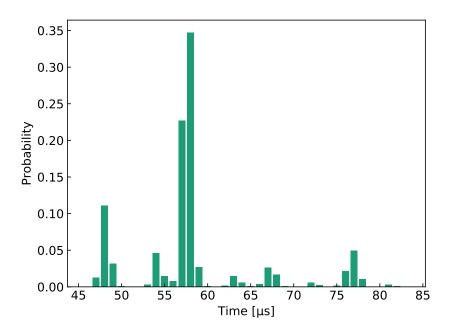

| 5.2  | Sampling Interval Histogram of PAPI Framework        | 35 |

| 5.3  | Sampling Interval Histogram of Powercap Framework    | 35 |

| 5.4  | Sampling Interval Histogram of Custom Framework      | 36 |

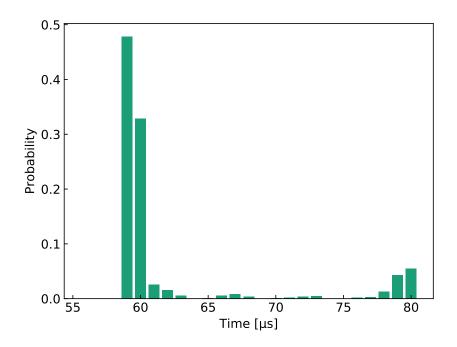

| 5.5  | Influence of the clock                               | 37 |

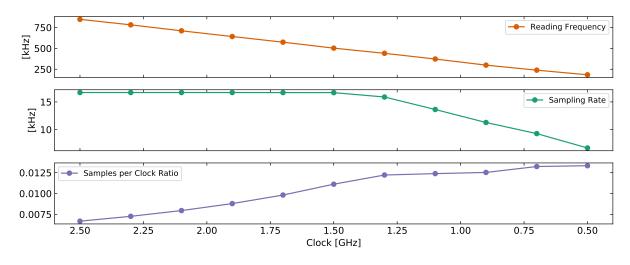

| 5.6  | Idle Energy vs Idle Power                            | 38 |

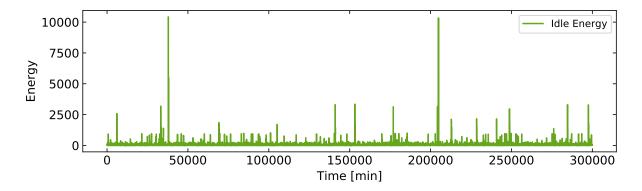

| 5.7  | Energy Spikes                                        | 38 |

| 5.8  | Long Idle Noise                                      | 39 |

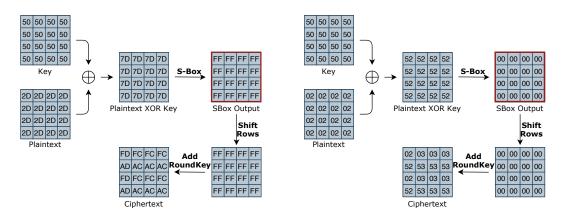

| 6.1  | Simplified AES                                       | 42 |

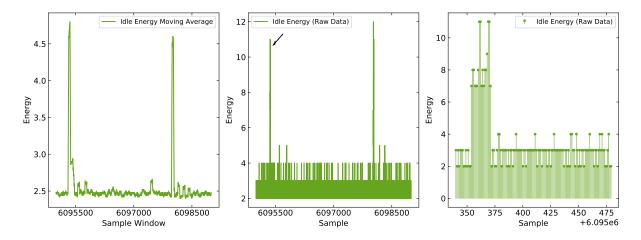

| 6.2  | Acquisition Method - 0x00's vs 0xFF's                | 43 |

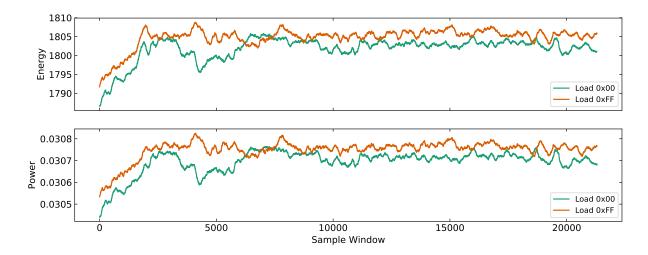

| 6.3  | Energy and Power Moving Averages of 0x00's vs 0xFF's | 43 |

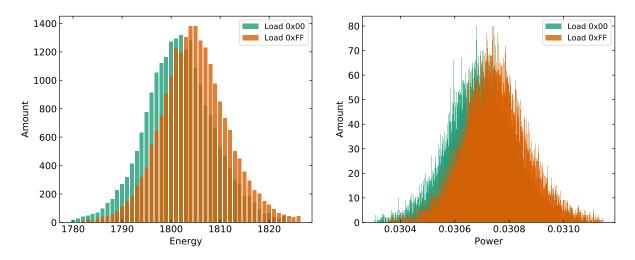

| 6.4  | Energy and Power Histograms of 0x00s vs 0xFF's       | 44 |

| 6.5  | Power vs Energy                                      | 47 |

| 6.6  | Comparison of Grouping Value and Filters             | 48 |

| 6.7  | Machine WarmUp                                                               | 49 |

|------|------------------------------------------------------------------------------|----|

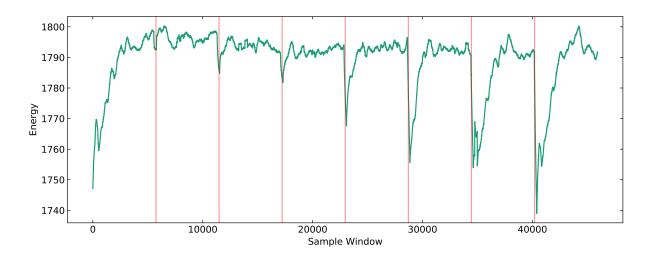

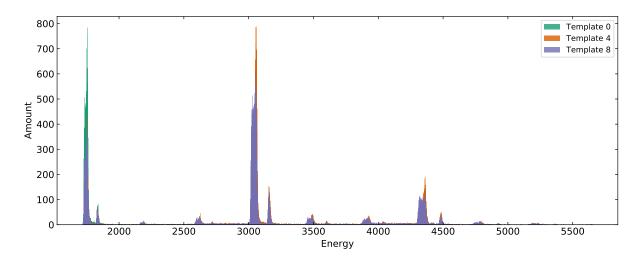

| 6.8  | Acquisition with Processes Running                                           | 51 |

| 6.9  | Sampling Interval Histogram of Custom Framework in other machine             | 52 |

| 6.10 | Histograms for Simplified Scenario in a different CPU                        | 52 |

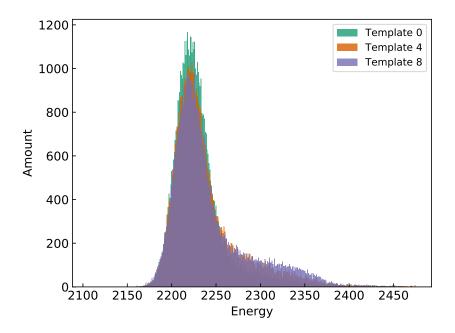

| 7.1  | Template Attack against AES                                                  | 55 |

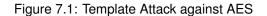

| 7.2  | Simulated Attack                                                             | 56 |

| 7.3  | Key ranking per error rate and number of plaintexts for Templates 0, 4 and 8 | 57 |

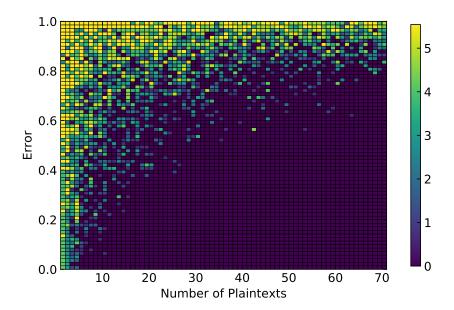

| 7.4  | Key ranking per error rate and number of plaintexts for 5 and 9 Templates    | 59 |

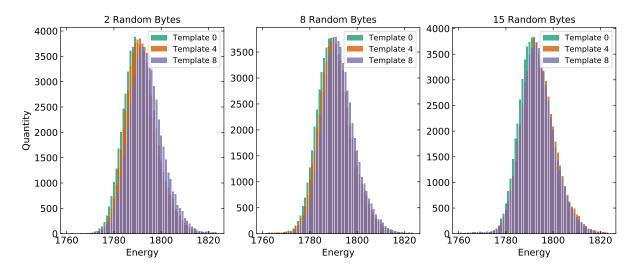

| 7.5  | Distributions with Different Number of Random Bytes                          | 60 |

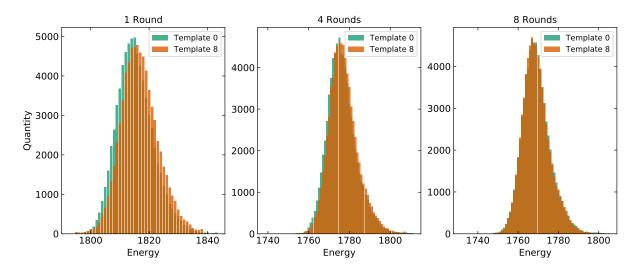

| 7.6  | Distributions with Different Number of Rounds                                | 61 |

## Acronyms

- ADC Analog-to-Digital Converter. 18, 37, 39, 63, 64

- AES Advanced Encryption Standard. xv, 7, 10, 20, 21, 23, 25, 26, 31, 32, 41, 45, 53, 55, 59–61, 63, 64

- CMOS Complementary Metal-Oxide Semiconductor. 15

- CPA Correlation Power Analysis. 22, 45

- CPU Central Processing Unit. xvi, 2, 10, 11, 16, 17, 24, 29–31, 33, 34, 36, 37, 39, 50–53

- DES Data Encryption Standard. xv, 10, 19, 20

- DPA Differential Power Analysis. 19, 20, 22, 23, 26

- **DSA** Digital Signature Algorithm. 6

- HO-DPA High-Order Differential Power Analysis. 26

- MAC Message Authentication Code. 6

- MCC Matthews Correlation Coefficient. 46, 50

- MSR Model Specific Register. 33–36, 44

- PAPI Performance Application Programming Interface. 17, 33–36, 63

- Pols Points of Interest. 23-25

- RAPL Running Average Power Limit. 2, 17, 26, 29, 37, 39, 47, 50, 51, 53, 63, 64

- RSA Rivest, Shamir and Adelman. 6, 10, 26

- SCAs Side-Channel Attacks. 1, 9, 10, 19, 26

- SNR Signal-to-Noise Ratio. 18, 30, 31, 39

- SPA Simple Power Analysis. 19, 20

### **Chapter 1**

# Introduction

There are very two significant aspects among many others that characterise and distinguish our era from the past. These are the amount of available information and the connectivity among people. On one hand, there is an on-going process of digitalisation: information is being stored in digital format, possessing an inestimable price in different aspects besides the economic one. On the other hand, we live permanently connected and in communication with each other through the internet, with efforts being made to bring most devices to a network, forming for example the so-called Internet of Things. All this makes the cyberspace more and more relevant, valuable and real. And like in anything that is valuable and real, threats and risks surge. This way, Information Security rises as an extremely important area of today's society, being crucial for different sectors such as communications, economics, health systems, and even our own entertainment.

Information Security is based upon three fundamental and equally-important pillars: confidentiality, integrity and availability. Confidentiality is the property that imposes that information is only available to authorised users. Integrity of data assures it's accuracy and completeness during it's existence, that is that it can't be modified in an unauthorised way. Finally, availability means that the information is accessible when needed.

These pillars are constantly challenged by the discovery of new vulnerabilities and the creation of new attacks. In order to protect the information from unauthorised parties and therefore ensure confidentiality and integrity, the data is many times encoded or, in other words, encrypted. The area that studies the methods and algorithms to encrypt data is Cryptography. Due to its importance and past study, there are widely-used algorithms that are mathematically very secure. Given the difficulty to break such algorithms, the current strongest attacks don't target the algorithm itself, but it's physical implementation, that is device-dependent and consequently more difficult to protect. These are the so-called Side-Channel Attacks (SCAs). Examples of this kind of attacks use channels like electromagnetic emissions, power consumption or sound to discover the secret information.

Parallel to the increasing technology presence comes the concern of energy usage, both from an environmental point of view and from an economic perspective, especially in big data centers. One example of this aspect is the strategic placement of cryptocurrency mining farms in colder parts of the

globe in order to lower the energy expenses related with cooling the computers. Another, being both an example and a consequence, is the inclusion of power meters in modern processors, in order to monitor and limit their energy consumption. In Intel's processors, this feature is named Running Average Power Limit (RAPL) and is included in all chips since the Sandy Bridge architecture. Bringing this together with the side-channel attacks that exploit the power consumption, the possibility of new threats arise.

#### 1.1 Objectives

The objective for this work is to study the possibility of using the processors' energy measurement counters to create a power analysis side-channel attack. This can be separated into two main goals: first, the information leakage regarding sensitive information of the encryption operations has to be detected through those counters; then, that leakage has to be quantified in order to measure the threat if represents. A parallel goal of this dissertation is the exploration of possibilities for this emerging field.

#### 1.2 Main Contributions

The contributions proposed to tackle those objectives are:

- Characterising the processors' energy counters' measurement capabilities, using the Running Average Power Limit (RAPL) interface of an Intel's Skylake architecture as a practical example;

- Acquisition of power consumption profiles using the mentioned counters;

- Study and evaluation of the required parameters and processing techniques to create a real sidechannel attack;

- Design and evaluation of an actual prototype attack;

- · Concluding about the threat of energy measurement interfaces towards information security.

#### 1.3 Thesis Outline

This dissertation starts by analysing the background required for side-channel attacks from both a cryptographic point of view and a CPU architecture one. This way, in the first half of Chapter 2 some cryptographic concepts are exposed, namely its different usages, types and algorithms, as well its threats and attacking methods. In the second half, the hardware and functioning of a CPU is analysed with attention given to the origin of the energy leakage explored in this work, and current measurement methods are described.

The state of the art is described in Chapter 3, presenting the origins and important techniques used for side-channel attacks, as well as the countermeasures.

Chapter 4 describes the methodologies of this study and the procedures to follow, including the reasoning behind the chosen paths.

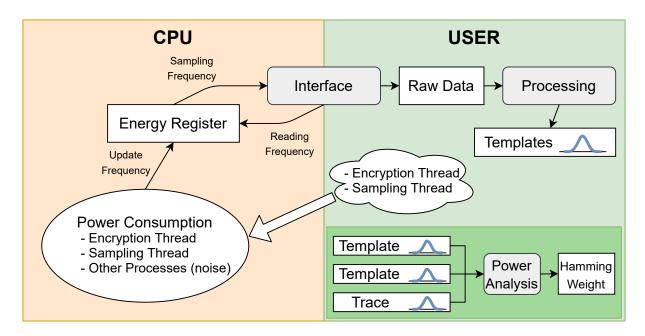

In Chapter 5 the energy measurement interfaces are characterised together with the respective measures in order to define the most promising one. Some properties such as the sampling, update and reading frequencies are defined and clarified, and other parameters are tuned.

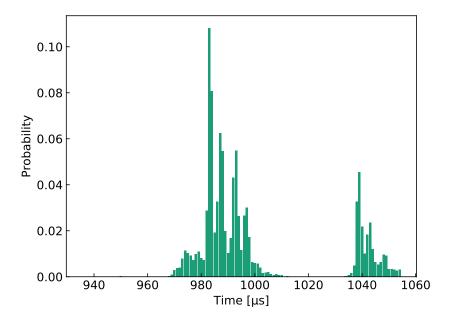

Following that analysis, in Chapter 6 a scenario to detect leakage is created and put to test, allowing the construction of methods to process the acquired data and create and differentiate templates. A small comparison is done using the same techniques applied on other systems.

Having successfully detected the leakage, the complexity of the scenario is increased in Chapter 7 in different ways towards a real-case one, and the limits of the defined attack regarding that complexity are drawn. A study is done towards the possibility of bypassing those limits.

Finally, in Chapter 8 a conclusion is presented with the key achievements of this dissertation, together with the future work for this emerging topic.

### Chapter 2

# Background

#### 2.1 Cryptography

Cryptography is the area of Information Security that deals with protecting sensitive information from unauthorised users. This information can be anything from resting data files, to messages, passwords, among others. This way, cryptography allows the secure transmission of information through insecure channels, in order to ensure confidentiality. Cryptography is also used to digitally sign data or create message authentication codes to provide authentication and integrity. It is used everyday in many forms of technology, like the internet, Bluetooth, mobile telephones, wireless systems, bank ATM's, among others; many times without the average user even noticing it.

The means to implement cryptography are the cryptographic algorithms. These algorithms encrypt data, referred to as plaintexts, by transforming them into incomprehensible ciphertexts. That transformation is based on a secret value, referred to as the key. The inverse operation, called decryption, transforms the ciphertext back into the plaintext, that is the original data. Again, a key is needed to perform this operation. Here, cryptographic algorithms branch into two families: Symmetric Cryptography and Asymmetric Cryptography.

#### 2.1.1 Symmetric Cryptography

In Symmetric Cryptography, the same key is used to encrypt and decrypt. Therefore, it is shared among the parties related to the information. This kind of algorithms are usually more efficient and used to encipher blocks of data. The main disadvantage is that sharing a secret key between different parties can be tricky, especially if there are no secure channels to communicate, which is a realistic assumption.

Encryption algorithms of this family mostly rely on *Feistel* or *Substitution-Permutation* networks to create *block cipher algorithms*, that are therefore combined via different *modes of operation*. The plaintext is divided into fixed-size blocks, and each part is ciphered by the block cipher. The mode of operation provides a chaining rule according to which the blocks encrypted or decrypted depend on the previous or next. This avoids an independent block-by-block operation that would make the ciphertext reveal undesired information about the plaintext.

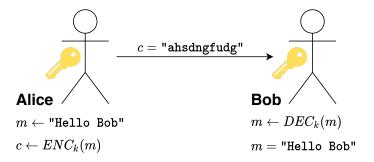

Figure 2.1: Alice sends a message to Bob using symmetric cryptography. The two parties have the same key.

To provide authentication and integrity, a Message Authentication Code (MAC) can be sent together with the message. It consists of a short piece of information generated by the shared key and the message. This way, the receiving party can generate a MAC with the received message and the own shared key, and compare it with the received MAC, detecting any changes to the original message.

#### 2.1.2 Asymmetric Cryptography

Asymmetric Cryptography relies on the use of a pair of related keys, generally referred as the public key and private key. The first key is publicly known, while the second is a secret known only to the corresponding party. This way, if anyone wants to communicate with that person, the messages can be encrypted with the known (public) key, ensuring that only that entity has the private key to decrypt that message. While being less efficient, there is the advantage of allowing communication through insecure channels, since no secrets need to be shared.

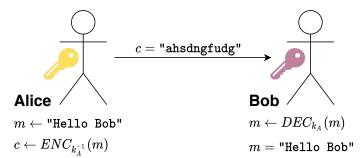

Figure 2.2: Alice sends a message to Bob using asymmetric cryptography. The two parties have two different keys of a key pair.

Asymmetric Encryption algorithms rely on mathematical problems such as the factorization of the product of two large prime numbers (RSA), or the discrete logarithm problem (El Gamal System). DSA is another example of this kind of algorithms.

To ensure authentication and non-repudiation, Digital Signatures can be used. For that, one party can use the private key to encrypt a message. This way, by decrypting it with the corresponding public key, the receiving entity is certain that the message author is correct. Contrary to the Message Authentication Codes, this method also provides non-repudiation since no one else has the private key: the person can

not deny having signed the message.

It is very usual to use asymmetrical algorithms to encrypt a key to send it to the receiving entity, and then use that key as a shared secret to symmetrically encrypt the data.

#### 2.1.3 Advanced Encryption Standard (AES)

The Advanced Encryption Standard (AES) is the most commonly used symmetric algorithm for cryptography. It is a fixed-size block chipher of 128 bits, with different options for the key size: 128, 192 or 256 bits, being therefore often referred as AES-128, AES-192 or AES-256. It consists of a loop of rounds of a *substitution-permutation network*, where the operations are sequentially applied to the original plaintext, called state. This state is viewed as a  $4 \times 4$  matrix of bytes. The number of rounds depends on the key size, being 10, 12 and 14 accordingly for the 128, 192 and 256-bit versions, with a slightly different last round. For each round there is a *subkey* (or *roundkey*) derived from the main key though a *key scheduler*.

**input** : 128-bit Block of Plaintext; 128/192/256-bit Key **output:** 128-bit Block of Ciphertext

- 1 KeyExpansion;

- 2 AddRoundKey;

- ${}_{3}$  for 1 to  ${}_{9}/{}_{11}/{}_{13}$  do

- 4 SubBytes;

- 5 ShiftRows;

- 6 MixColumns;

- 7 AddRoundKey;

- 8 **end**

- 9 SubBytes;

- 10 ShiftRows;

- 11 AddRoundKey;

Figure 2.3: Advanced Encryption Standard Overview - Encryption

The performed operations are:

#### KeyExpansion

RoundKeys are derided from the main key through the AES Key Schedule, which is the algorithm that expands the input key into several. One RoundKey is generated per round, being the first round key equal to the input key.

#### AddRoundKey

Bitwise Exclusive-OR (XOR) between State and RoundKey:  $State \oplus RoundKey$

#### SubBytes

Substitution of each State byte  $a_{i,j}$  based on a *Substitution-Box* (S-Box), in the form  $a_{i,j} = S(a_{i,j})$ . The S-Boxes are fixed tables, so that this step provides non-linearity to the algorithm.

#### ShiftRows

Cyclically shifts to the left the bytes of each row n times, being n = 0, ..., 3 the number of the row. This step assures that the columns are not encrypted independently.

#### **MixColumns**

Combines bytes of each column independently based on a invertible linear transformation in the finite field  $GF\{2^8\}$  given by a fixed matrix, in the form

$$\begin{bmatrix} b_{0,j} \\ b_{1,j} \\ b_{2,j} \\ b_{3,j} \end{bmatrix} = \begin{bmatrix} 2 & 3 & 1 & 1 \\ 1 & 2 & 3 & 1 \\ 1 & 1 & 2 & 3 \\ 3 & 1 & 1 & 2 \end{bmatrix} \begin{bmatrix} a_{0,j} \\ a_{1,j} \\ a_{2,j} \\ a_{3,j} \end{bmatrix} \quad j = 0, .., 3$$

$$(2.1)$$

This step, together with the previous, provides diffusion to the network.

For decryption, the inverse operations are applied in the reverse order to restore the original plaintext from the ciphertext are represented in algorithm 2.4. The roundkeys order is also reversed, to match the corresponding round.

input : 128-bit Block of Ciphertext; 128/192/256-bit Key output: 128-bit Block of Plaintext

- 1 KeyExpansion;

- 2 AddRoundKey;

- 3 InvShiftRows;

- 4 InvSubBytes;

```

{\scriptstyle 5}\, for 1 to 9/11/13 do

```

- 6 AddRoundKey;

- 7 InvMixColumns;

- 8 InvShiftRows;

- 9 InvSubBytes;

10 **end**

11 AddRoundKey;

Figure 2.4: Advanced Encryption Standard Overview - Decryption

#### 2.1.4 Cryptanalysis

Contrary to cryptography there is *cryptanalysis*, referring to attacks that try to recover the secret information manipulated by a cryptographic algorithm, which can be either the key, the plaintext or ciphertext, or some key-dependent data that the attacker can use instead of the key. The goal is to improve the time or computational resources it takes to retrieve sensitive information, from the worst case scenario *Brute Force Attack*. This is considered the most trivial cryptographic attack, where every possible key is tried one by one. This attack is unfeasible for most cases, since current algorithms usually use keys with a size of 128 or more bits that make such search an impossible task with even the most recent technology. Different adversary models can be considered in cryptanalysis, based on the amount of information available to the attacker. For instance, knowing some plaintext/ciphertext pairs, the algorithm or the key size are all variables that are considered. It is generally assumed that the attacker has a perfect knowledge of the algorithm.

Two well known and broad adversary models are the *Black-Box model* and the *Grey-Box model*. Other models exist, but are beyond the scope of this work.

**Black-Box Model.** The first adversary model illustrated in 2.5 is the more traditional, which assumes that the attacker only has access to the inputs and outputs of the operations, e.g, the plaintexts and ciphertexts. It aids revealing if an algorithm is mathematically secure, independently of the physical implementation. In fact, modern used encryption algorithms are considered or proved secure against attacks based on this model. The already mentioned *Brute Force Attack* is an example of an attack based on this model.

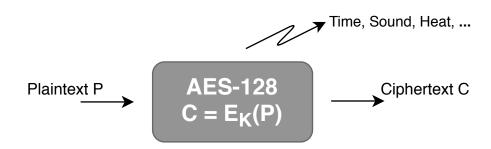

$$\xrightarrow{\text{Plaintext P}} AES-128 \xrightarrow{\text{Ciphertext C}} Ciphertext C$$

Figure 2.5: Black-Box Model - The adversary can choose plaintexts and/or ciphertexts to try to mathematically break the known algorithm.

**Grey-Box Model.** In the second model, represented in figure 2.6 the attacker may have access to the physical device where the cryptographic algorithm is implemented. This way, this model illustrates more accurately most real systems, since it is tied to the physical world where devices reside. The attacker may have access to the physical information leaking, such as power consumption, time, or radiation. The resulting attacks are called Side-Channel Attacks (SCAs), introduced in the following section.

Figure 2.6: Grey-Box Model - In addition to the Black-Box model possibilities, the adversary also has access to the physical implementation of the device.

#### 2.1.5 Side-Channel Attacks

Side-Channel Attacks (or Physical Attacks) are a family of attacks emerging in the late nineties that exploit the weaknesses of the physical implementation of a cryptosystem, instead of attacking the algorithm itself. This uses the fact that while an algorithm might be mathematically secure, it can be leaking

other types of information through its implementation, ignored in the Black-Box model. These attacks can be much more powerful than traditional Black-Box attacks, and present an ever increasing threat to cryptosystems. In fact, most actual cryptographic algorithms have been broken with Side-Channel Attacks. The origin of these attacks date back to 1996, when Kocher [1] broke RSA and Diffie-Hellman systems (asymmetrical encryption algorithms) based on the time it took to perform the operations. Three years later, as described in [2], he used power measurements to break DES (the most commonly used symmetrical encryption algorithm at the time), and proved capable of doing so on other algorithms. This new *Power Analysis* attack has been used across different implementations, such as Smart-Cards [3], FPGAs [4], to even more recent smartphones [5]. In [6], AES is broken using the timing it takes to encrypt due to cache hits and misses. It is an example of cache-timing attacks. Several other attacks based on caches have been successful [7]. Other interesting type of side-channel attacks abuse the device to make it leak information under subnormal conditions, such as the Fault Injection attack [8]. More attacks exploiting other leakage information exist, like electromagnetic radiation or sound.

Following Mangard, Oswald, and Popp [3], SCAs can be further categorised in different ways, according to the adversary's capabilities, the available equipment and their complexity. They are distinguished between active/passive attacks, and invasive/non-invasive ones, being this categories orthogonal to each other.

Active attacks exploit abnormal behaviours in the devices, sometimes by tempering with it, in order to obtain secret information in a way that would not be possible under normal usage. Examples include overheating the device, variations in the power supply voltage level and irregularities in the clock signal [8]. On the other hand, passive attacks are done under normal behaviour of the device.

Invasive attacks require a permanent action on the device by the attacker. This means that the attacker is able to physically access the chip and its underlying components. This way, direct contact can be established with the chip to recover sensitive information. On the contrary, non-invasive attacks can have access to the external component but cannot modify them in any way. It is restricted to observing the activity, with the possible aid of tools that don't alter the device, such as timers and oscilloscopes.

Given the importance of this family of attacks, under which most cryptographic algorithms have failed to resist when not properly protected, a big concern is given to the corresponding countermeasures. These can range from software changes to big hardware modifications. In this work emphasis is given to power consumption attacks in a non invasive way and the corresponding countermeasures.

#### 2.2 Computational Architecture

The Central Processing Unit is the component of a computer responsible for performing different instructions. This instructions are the steps executed by the processor to perform the operations provided by a computer program in order to do any task. This way, usual programming languages in which programs are written are ultimately translated to a low-level programming language called *assembly*, which has a strong correspondence to what the computational architecture actually does at the architectural level. This assembly code is then *assembled* into executable machine code instructions by an *assembler*, specific for the processor in question. Those instructions are then executed, performing the desired tasks, such as arithmetic operations or data manipulation. This logic and physical design, together with its organisation and implementation, is called a microarchitecture.

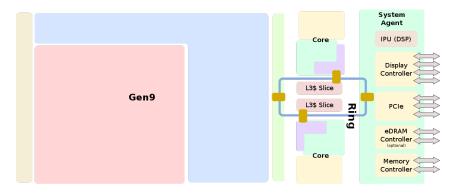

There are significant differences across CPUs, leading to a range of different performances and targeted usages. One important characteristic is the clock rate which refers to the frequency at which the components of the processor operate, in order to synchronise them. This directly reflects on the performance of the processor, as it determines the number of instructions performed per time unit. In an attempt to further increase the processing speed, most computers' have a microprocessor chip with several processors inside them, called *cores*. Figure 2.7 illustrates a diagram of Intel's Skylake chip, containing two cores. This specific client configuration is designed for desktops and personal computers, and there is also a server configuration aimed towards workstations, with up to 28 cores [9]. Alongside the cores which process and perform the instructions, there are other components with different functions. These include the *integrated graphics unit*, which can be seen as a core dedicated to image processing and output, and the *system agent*, which deals with other tasks crucial to the processing such as memory management and control. Surrounded by all this components it's the last-level-cache, which corresponds to a portion of memory shared by all the cores. Finally, the interconnect ring connects the components of the chip.

Figure 2.7: Diagram of Intel's Skylake Dual-core Chip (Client Configuration), from *WikiChip.org*. The chip contains two processing cores, the integrated graphics, the system agent and the last-level cache, all connected through a ring connection.

#### 2.2.1 Instruction Set

Intel's processors of the *x86* class support the *x86 instruction set* (corresponding to the *x86 Assembly Language*), which is expanded as new processors and instruction packs are released. Other manufactures have a different instruction set, which serves the same purpose and functions in a similar way. These instructions are represented by a mnemonic that is possibly combined with one or two operands, being then translated to a series of bytes called an *opcode*. The operands correspond to the places where the values used in the operation are stored, called *registers*. The *opcodes* are read and processed by the CPU and generally represent a single executable machine instruction.

In Table 2.1 several examples of assembly instructions are illustrated. The mnemonic specifies the

| MOV EAX, 1 | Moves the value 1 to the register EAX                    |

|------------|----------------------------------------------------------|

| ADD BX, AX | Stores in register BX the sum of the values in BX and AX |

| NOP        | No Operation                                             |

| JMP EAX    | Jump to the value stored in the register EAX             |

Table 2.1: Some examples of simple x86 instructions. Some instructions have no operands, while others have one or two. Note that the storing place of arithmetic operations is over one of the operands.

instruction to be performed, and may require operands or not. To store binary data in order to read and write the result of a command, modern Intel's processors include a collection of 16 64-bits registers. Some of them have a specific usage usually assigned to them, such as the ESP that is used to store a pointer of the topmost element in the stack. Others have no such usage, and are free to store and read data.

There are several instruction types that the x86 instruction set covers, as illustrated in Table 2.2

| Stack                      | Set up stack to pass parameters to functions, allocate space for data and restore call-return points.                         | push, pop                      |  |  |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--|--|

| Data Handling              | Data loading and storage, setting a register to a constant value                                                              | mov                            |  |  |

| Arithmetic and Logic       | Standard arithmetic and logical operations, on integers or floating points, setting status register flags accordingly         | add, div, and,<br>or, shl, shr |  |  |

| Control Flow               | Branch to another location of code, directly, indirectly or conditionally. Call another block of code to implement functions. | jmp, int, call                 |  |  |

| Others: SIMD               | Performing an operation on many homogeneous values in parallel, for vector manipulation.                                      | vmul, psllv                    |  |  |

| Others: Crypto-<br>graphic | Performing encryption/decryption and other cryptographic functions in dedicated hardware                                      |                                |  |  |

Table 2.2: Different types of x86 Instructions and their usage, together with some examples.

#### 2.2.2 Workflow of a Core

In order to perform the different types of instructions in the most efficient way, a series of components exist inside a processor. Figure 2.8 illustrates the block diagram of a core from Intel's Skylake microarquitecture. The core can be separated into two main areas: the *Front End* and the *Execution Engine*, and the auxiliary *Memory Subsystem*.

#### Front End

The goal of the Front End is to feed the Execution Engine with a stream of operations it gets by decoding instructions coming from memory. The life-cycle of an instruction starts in the *L1 Instruction Cache* after being loaded from memory. At this point, the instructions are organised as *macro-operations (macro-ops)*, which are variable-length instructions. For each clock cycle, a maximum of 16 bytes of code (corresponding to a maximum of 6 *macro-ops*) are fetched from that cache into the *PreDecode*

Figure 2.8: Diagram of a Processor's Core, from *WikiChip.org*. The different components are organized into a complex system with the goal of optimizing the security, speed and performance of the instruction flow.

*buffer*, where the corresponding boundaries are detected and marked. The pre-decoded instructions are consequently delivered to the *Instruction Queue*, which holds a maximum of 50 entries before being sent to the *Instruction Decoder*. In some cases two *macro-ops* are fused into a complex one, saving bandwidth in the remaining pipeline. Five instructions are sent to the decoder per cycle. Its main function is to transform the previous *macro-ops* into regular, fixed-length *micro-ops* ( $\mu OPs$ ), which are sent to the *Allocation Queue*. Some complex *macro-ops* instructions that transform into more than 4  $\mu OPs$  are

routed through the *Microcode Sequencer ROM* before proceeding, as it proves faster this way than decoding such commands. All this happens in parallel with the *Branch Predictor*, which inspects code further in the byte stream and tries to predict the flow of instructions, and may also send instructions to the *Allocation Queue*. Those instructions are stored in the  $\mu OP$  Cache, and a hit there allows for up to 6 *micro-ops* being sent directly to the *Allocation Queue*, bypassing most of the pipeline and saving important resources and bandwidth. One final component of this part of the processor workflow is the *Stack Engine*, which operates commonly used stack-instructions such as the *POP* or *PUSH* in order to save resources in the back-end.

The *Allocation Queue* acts as an interface between the *front-end* and the *back-end*. Following the previous description, this first works *in order*, meaning that the processing of instructions respect their chronological order in the instruction flow. The same does not apply to the latter, which operates in an out-of-order fashion. This way, the *Allocation Queue* purpose is to effectively dissipate clusters of similar operations that can not be performed simultaneously, ensuring a steady stream of 6  $\mu$ OPs delivered each cycle to the *Reorder Buffer (ROB)*.

#### **Execution Engine**

In the *ROB*, several bookkeeping tasks are done in order to proceed with the instruction. This includes mapping the architectural registers onto the physical ones and allocating resources for data manipulation. The *Register Alias Table* aids in the register renaming by storing where the data is coming from, in terms of previous instructions. At the same time, the *Branch Order Buffer* keeps track of the architectural state in case a roll back is necessary, which is something normal as this processor performs speculative execution. After the *ROB*, instructions proceed to the *Scheduler* where they wait in a queue to be executed. This wait can be due to two reasons: either one required operand has not arrived because it is being loaded or calculated, or the required execution unit is busy. There are eight available ports departing from the *Scheduler*, that lead to different execution units. This means that in the same clock cycle one instruction can be executed from each port, resulting in a total of eight simultaneous instructions assuming they do not require the same execution units. Table 2.3 describes the available operations according to the port of this architecture's scheduler.

After being executed,  $\mu$ OPs are retired in the *Reorder Buffer*, releasing any used resources related to them. This happens *in-order*, so the chronological order of the instructions is re-established.

#### Memory Subsystem

The memory subsystem controls the load and store requests and ordering. Some buffers exist to support those tasks, namely *Load Buffer*, *Store Buffer* and the auxiliary *Line Fill Buffers*. Different types of memory exist in a processor regarding its size, speed and price characteristics. This allows for a good way of balancing different speed and size requirements while achieving a good performance. Skylake has three levels of data cache, which are denominated L1, L2 and L3 (or Last-Level-Cache) as their size increases and their speed decreases. When a piece of data is requested for processing, the L1 cache is inspected as it is the fastest to deliver the request. If the data is found there, then a *cache hit*

| Execution Unit             | Port 0 | Port 1 | Port 5 | Port 6 | Port 2 | Port 3 | Port 4 | Port 7 |

|----------------------------|--------|--------|--------|--------|--------|--------|--------|--------|

| Integer Arithmetic/Logic   | X      | Х      | Х      | Х      |        |        |        |        |

| Vectorial Arithmetic/Logic | X      | Х      | Х      |        |        | Х      |        |        |

| Integer Multiplication     |        | Х      |        |        |        |        |        |        |

| Vectorial Multiplication   | X      | Х      |        |        |        |        |        |        |

| Integer Division           | X      |        |        |        |        |        |        |        |

| Floating-Point FMA         | X      | Х      |        |        |        |        |        |        |

| Floating-Point Division    | X      |        |        |        |        |        |        |        |

| AES Operations             | X      |        |        |        |        |        |        |        |

| Vectorial String Ops       | X      |        |        |        |        |        |        |        |

| Vectorial Shuffle Ops      |        |        | Х      |        |        |        |        |        |

| Bit Scan                   |        | Х      |        |        |        |        |        |        |

| Load Effective Address     |        |        | Х      |        |        |        |        |        |

| Address Generation         |        |        |        |        | Х      | Х      |        | Х      |

| Branch                     | X      |        |        | Х      |        |        |        |        |

| Store Data                 |        |        |        |        |        |        | Х      |        |

| Load Data                  |        |        |        |        | Х      | Х      |        |        |

Table 2.3: Operations available at the execution units routed by each port of the Scheduler. While some operations such as Integer Arithmetic can be performed four times during the same clock cycle (using different operands), others such as Data Storage are limited to one.

occurs and the request is processed in the fastest way. However, if the data is not found, a *cache miss* happens and the request proceeds to the L2. Here the same procedure happens, and so on. When the request is found, it is stored in a closer cache to allow future access, under certain restrictions and control. Data caches allow for much faster processing because it is common for the same data to be requested several times.

#### 2.2.3 Energy Consumption

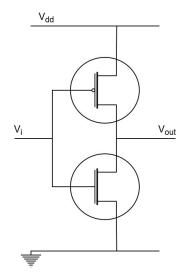

Digital circuits operate based on two levels of discrete voltage levels, labelled *0* and *1*. To implement the Boolean (binary) logic, operations are done through *logic gates*. These are electronic devices that implement some Boolean function, producing an output (0 or 1) based on its input. They serve as the building block for more complex devices, such as multiplexers, registers and memory, until complete microprocessors. Despite existing different ways of implementing those logic gates, the Complementary Metal-Oxide Semiconductor (CMOS) transistors technology is by far the most used. In fact, in 2011, 99% of all integrated circuit chips were fabricated with this technology [10].

The relevant advantage of CMOS over the concurrent technologies regarding this work is the low power dissipation. This is possible due to the complementary pull-up and pull-down network organisation, which is arranged such that when one is activated, the other is disabled. This results in a static consumption power near zero, as the path between the power source and the ground is not connected during idle moments. The main source of power consumption is then the dynamic part, which corresponds to the energy that is consumed during the transitions of state. These transitions result in brief moments when both networks conduct and the connection between the power source and the ground the ground is not connected the power source and the ground is not connected during the transitions of state.

Figure 2.9: CMOS Inverter Gate. When the top transistor is activated the bottom one is disabled, disconnecting the path between the power source and the ground.

is established, resulting in energy dissipation. Other minor sources of power consumption include the transistor leakage currents, that correspond to the energy that flows through a boundary seen as insulating, and short-circuit power consumption, that is related to brief short-circuits across transistors during a state change of a logic gate.

Power consumption sources are complex and depend on many factors, from the physical properties of the transistors to external conditions like the temperature, being therefore difficult to model precisely. It is known that the dynamic and short-circuit fractions of the power consumption are proportional to the clock frequency, while the leakage currents are proportional to the supply voltage. Despite that, the dynamic power consumption, being only consumed during transitions of state of a logic gate (and not on every clock cycle) is dependent on the data being manipulated. This includes the flow of instructions being processed in the whole processor, and the operands used in the execution units, stored in registers. Consequently, if the same algorithm is executed on different pieces of data, the power consumption is different due to the different values of the registers. For the same reasons, two different algorithms being executed with the same data will also have a different power consumption associated.

This correlation between the manipulated data and the power consumption provides a chance for the exploitation used in the already mentioned side-channel attacks. It should also be noted that the actual value of power consumption is usually irrelevant, as it is the relative differences that leak the sensitive information.

#### 2.2.4 Software-based Energy Measuring

With the growing amount of data centers and devices, together with the importance of saving energy or controlling its expenses, power consumption becomes a critical metric in the design and usage of electronic systems. With high-performance computing machines having hundreds or thousands of cores, reducing a few Watts per CPU quickly adds up to significant power, cooling and monetary savings [11]. This has led to the introduction of new components into CPUs that allow energy and performance

measurement, in order to measure or limit the consumption as necessary. Despite their importance, their consequences on information security are not completely understood[12].

In Intel's CPUs, this feature is covered by Intel's Running Average Power Limit (RAPL), which consists of a set of measuring sensors and counters, as described in the Intel Software Developer's Manual [13]. It is included in their CPUs since the *SandyBridge* microarchitecture, with slight differences across the many subsequent ones.

RAPL stores the energy values in different registers, according to the domain of the measurement. The domains refer to different parts of the processor:

- **Package** Measures energy consumption of the entire chip. This includes all the cores, integrated graphics, and *uncore* components such as last-level-cache operations and memory controllers.

- Power Plane 0 (PP0) Measures energy consumption of all the cores.

- Power Plane 1 (PP1) Measures energy consumption of the integrated graphics.

- DRAM Measures energy consumption of the random access memory attached to the integrated memory controller.

- Psys Measures energy consumption of the Package Domain, plus PCH, eDRAM, among others.

The units for the power, time and energy readings vary according with the microarchitecture, and are found in the register  $MSR_RAPL_POWER_UNIT$ . For example, in order to convert an energy measure to Joules, it has to be multiplied by  $1/2^{ESU}$ , with ESU being the value represented in the bits 8 to 12 of that register. For the Skylake microarchitecture studied in this work, the ESU has the value 14. This way, the measures are transformed to Joules after being multiplied with  $1/2^{14} = 61 \ \mu$ J. This corresponds to the minimum difference that two power/energy samples can have, and is refereed as the resolution. Other architectures such as the Haswell have a resolution of 15.3  $\mu$ J. Notice that a smaller resolution allows for more accurate measures, as smaller differences in the input signal can be detected. This way, the raw integers stored in the register have to be multiplied by the resolution to be transformed in Joules.

In order to read those registers, an interface has to be used. The most common one is the Intel's Performance Application Programming Interface (PAPI) [14]. There are other options, as well as the possibility of customising an interface to read the driver. The comparison of different interfaces is presented in Chapter 5.

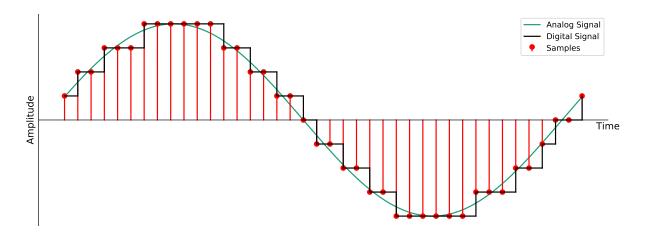

When dealing with the sampling of continuous signals such as the power consumption, it is important to consider the analog-to-digital conversion limitations and properties. Unlike the physical world, digital systems always deal with discrete values, as a result of their own representation in a stored number. This way, digital signals, and therefore any sampled signal, have a discrete time and a discrete amplitude. Such transformation from a continuous environment to a discrete one involves the *quantization* of the input signal, that is approximating real-world values with a digital representation of them, introducing necessarily an amount of *quantization* error, as represented in figure 2.10.

Another consequence of a discrete time environment is that the real signal is sampled periodically, limiting the allowable bandwidth of an input signal. The frequency at which the signal is sampled is called

Figure 2.10: Quantization of a Signal. The digital signal differs from the analog input as it uses only certain values - the quantization levels.

the *sampling rate*. This constitutes two main characteristics of an Analog-to-Digital Converter (ADC). In order to allow for a correct reconstruction of a sampled signal and assure that no information is lost, the Nyquist Theorem states that the sampling rate must be at least two times the maximum frequency of a signal. The phenomena of a reconstructing signal differing from the original one is called *aliasing*.

ADCs have some important characteristics that indicate their overall behaviour, such as the already mentioned sampling rate and resolution, and the Signal-to-Noise Ratio (SNR), that corresponds to the ratio between the power of the input signal and the power of the background noise. In the usual cases where the noise cannot be separated from the signal, the SNR is given by

$$SNR_{dB} = 10\log_{10}\left(\frac{P_{S+N} - P_N}{P_N}\right)$$

(2.2)

where  $P_{S+N}$  is the power of the meaningful signal plus noise, and  $P_N$  is the power of the noise alone. The power of a digital signal can be calculated with

$$P_s = \frac{1}{N} \sum_{k=0}^{N-1} |s(k)|^2$$

(2.3)

with N being the number of samples of the signal s.

This SNR is also influenced by a group of other characteristics like the non-linearity or the jitter.

The *non-linearity* affects all ADCs and refers to the errors caused by the physical imperfections that result in the output signal deviating from a linear function. The *jitter* comes from the small time differences of each clock cycle that lead to some uncertainty in the sampling interval. While non-existing at DC measures, its effect is significant at high-frequency acquisitions.

# **Chapter 3**

# State of the Art

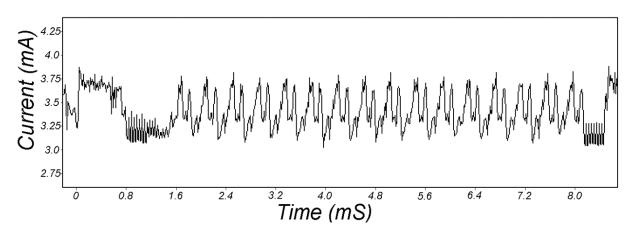

### 3.1 Power Analysis

Power Analysis is the branch of Side-Channel Attacks in which the channel used for exploitation is the power consumption of a device. Given that the instantaneous power consumption is usually dependent on the data being processed and on the instructions being performed, a proper analysis of the power consumption during the encryption or decryption operations can reveal leaked sensitive data, including the secret key. The first Power Analysis attack was published in 1999 by Kocher, Jaffe, and Jun [2], where the power consumption was measured with an oscilloscope and used to successfully break the DES algorithm, that was the most widely used encryption algorithm at that time.

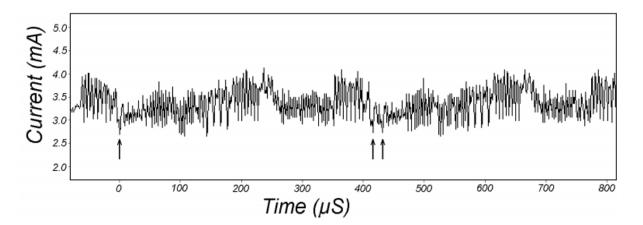

Most Power Analysis attacks are based on acquiring *power traces*, which are a set of consumption measurements taken during the execution of one cryptographic operation. This results in a sampled power consumption plot, as the one in Figure 3.1.

Figure 3.1: Power trace during one encryption with the DES algorithm on a Smart-Card, retrieved from [2]. The pattern of 16 similar oscillations represent the 16 rounds of the DES algorithm.

Different techniques exist to extract sensitive information from the power traces, branching Power Analysis into Simple Power Analysis (SPA) and Differential Power Analysis (DPA), or other types of attacks, such as the Template Attacks.

### 3.1.1 Simple Power Analysis

The simplest kind of Power Analysis Attacks are grouped under the name Simple Power Analysis. They exploit the information available at one or few power traces by visually interpreting it. For instance, in Figure 3.1, there is a clear pattern repeated 16 times, that correspond to the 16 rounds of the DES. That alone already provides a clue on the algorithm used.

Figure 3.2: Second and third rounds of DES, as a detail of 3.1 retrieved from [2]

In Figure 3.2 a more detailed view is shown, focusing on the second and third rounds of DES encryption. More details are visible, as we can see pointed by arrows: a certain operation (in this case a register rotation) was performed once in round two and twice in round three. Also, given the high power consumption of the conditional jump operation, by studying the flow of the algorithm and comparing with the analyzed plot one can guess the respective condition bit value. Other recognizable operations exist that leak data exploited through this technique.

Being SPA a not-so-recent technique, modern technology can easily evade this threat. Firstly, a smaller power consumption in components together with higher clock rates greatly increase the difficulty of interpreting the plots visually; and secondly, avoiding using sensitive information as a branching condition will obstruct most of the information.

### 3.1.2 Differential Power Analysis

A much more powerful form of attacks published in [2] consists of a statistical approach, usually referred to as Differential Power Analysis (DPA). In this case, the idea is to use information collected on many acquired consumption traces. It is used against algorithms in which the secret key K (or a subkey that derives from the secret key) is split in small parts, allowing a divide and conquer approach. Such is the case of most block cipher algorithms such as DES and the widely used AES.

To perform the attack, N power traces  $T = T_1, ..., T_N$  are acquired with W samples each, corresponding to the execution of the algorithm with N different plaintexts  $P = P_1, ..., P_N$ , and the same unknown key K. Let T[j] be the  $j^{th}$  sample of a given trace T. With the knowledge of the algorithm, the attacker can identify a intermediate bit that depends both on a small number b of key bits,  $K^*$ , and on the known plaintext P (or ciphertext). The number b must be small enough to allow a practically feasible brute force search with size  $2^b$ . Modelling the computation of that bit during the algorithm, a function is designed, taking as input those bits of the key and the respective plaintext. This function is called the *selection function*, with the form  $D(P, K^*)$ .

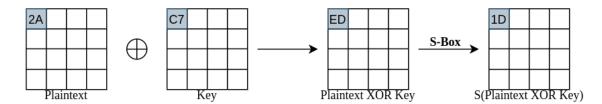

Figure 3.3: Selection function designed for AES to compute the first byte of the state after the *SubBytes* operation in the first round. The figure illustrates how it depends only on the first byte of the Plaintext, P[1], and on the first byte of the Key,  $K^*$ . For this algorithm, b = 8 is a good choice since the state is treated byte by byte. Note that the S-Boxes are fixed tables, and that the roundkey of the first round of AES is the secret key itself. The resulting function is  $D(P, K^*) = S(P[1] \oplus K^*)$ , with S being the S-Box substitution.

The attacker then separates each power trace T into two sets  $S_0$  and  $S_1$  according to the value of the most significant bit (MSB) of the *selection function* output, with the respective plaintext P and a given key part  $K^*$  as input. Finally, a *distinguisher*  $\Delta_D$  is applied to them. The one used originally by Kocher et al. consisted on calculating the trace corresponding to the difference of the averages of each set  $S_0$  and  $S_1$  as:

$$\Delta_D = \bar{S}_0 - \bar{S}_1 \tag{3.1}$$

This can be done sample by sample, assuming that the traces are synchronized in time, as

$$\Delta_D[j] = \frac{\sum_{n=1}^N MSB(D(P_n, K^*))T_n[j]}{\sum_{n=1}^N MSB(D(P_n, K^*))} - \frac{\sum_{n=1}^N (1 - MSB(D(P_n, K^*)))T_n[j]}{\sum_{n=1}^N (1 - MSB(D(P_n, K^*)))}$$

(3.2)

If the guessed key part hence designated as  $K^*$  is wrong, then the output  $\Delta_D$  will be a small noise near zero, since the result of the selection function D was different from the target for about half of the plaintexts. There is no correlation between the selection function and the actual computation done by the target device. Actually, as we increment the number of traces N, the better the averages will cancel each other and the closer  $\Delta_D$  will be to zero.

However, if  $K^*$  is correct, the output of the selection function will be the same as the one computed by the device for all the plaintexts, creating a correlation. As a result,  $\Delta_D$  will approach the effect of the target bit on the power consumption as N increases. The plot will be flat with spikes in the zones where D is correlated to the processed values. The attacker can then identify the correct key-part  $K^*$  by trying the method with all the  $2^b$  possibilities, and evaluating the computed  $\Delta_D$ .

By knowing one part of the key, the remaining bits can be guessed to allow discovering the respective missing parts. For this, it is used the 2nd byte of the key, and so on. The separation of the keys into different parts is what reduces the complexity of these kind of attacks to a feasible value. Given the case of AES-128, a brute force search for the whole 128-bit key would require  $2^{128}$  tries. However, splitting it

into 16 parts (1 byte each) and searching for each one individually on a space sized  $2^8 = 256$ , requires 16 \* 256 = 4096 iterations.

After this research work, many other works were proposed to complete and diversify this technique. Several other distinguishers have been compared [15, 16], such as the *Mutual Information Analysis* [17], the *Kolmogorov-Smirnov* [18] and the *T-Test* [19]. One of the them, probably the most widely used, is the *Pearson Correlation Coefficient*, explained in the following section.

### 3.1.3 Correlative Power Analysis

Correlation Power Analysis (CPA) uses the Pearson Coefficient of Correlation instead of the Difference of Averages as the *distinguisher* applied to the power traces set. It has numerous advantages, including the need for a smaller number of power traces [20].

Imagining the same situation as above, where there are N power traces  $T = T_1, ..., T_N$  with W samples each. Let  $T_n[j]$  be the  $j^{th}$  sample of the  $n^{th}$  power trance, with  $1 \le n \le N$  and  $1 \le j \le W$ . Corresponding to each power trace are N plaintexts  $P = P_1, ..., P_N$ , so that the trace  $T_n$  was measured while operating the  $P_n$  plaintext. Consider as well the same selection function  $D(P, K^*)$ , that computes an intermediate value with the plaintext, based on a key part  $K^*$  of b bits.

For CPA, a *Power Model* is defined for estimating the power. Because the dynamic power consumption depends on the number of bit changes, the *Hamming Distance* can be used for this model: the Hamming Distance (*HD*) between two binary numbers is the number of different bits, position-wise. This way, the *Hypothetical Power Consumption* can be computed with  $H_{n,k} = HD(D(P_n, K_k^*))$  for the  $n^{th}$  trace/plaintext pair and  $k^{th}$  possible key part, with  $0 \le k < 2^b$ .

Then, for each sample *j* and considered key part  $K^*$  the Pearson Correlation Coefficient  $\rho_{j,k}$  is calculated to measure the correlation between the *Hypothetical Power Consumption* and the real measures:

$$\rho_{j,k} = \frac{N \sum_{n=1}^{N} T_n[j] H_{n,k} - \sum_{n=1}^{N} T_n[j] \sum_{n=1}^{N} H_{n,k}}{\sqrt{N \sum_{n=1}^{N} T_n[j]^2 - (\sum_{n=1}^{N} T_n[j])^2} \sqrt{N \sum_{n=1}^{N} H_{n,k}^2 - (\sum_{n=1}^{N} H_{n,k})^2}}$$

(3.3)

The Pearson Correlation Coefficient outputs a value between -1 and 1. Higher absolute values mean that the two data sets compared have the best correlation, while a value of zero means that there is no correlation at all. The sign is not relevant for this case. Since the used data sets are the *Hypothetical Power Consumption* and the real power traces, the best correlation will most likely represent the correct key part. There is no need to separate the coefficients by sample, because time information about the moments in which that correlation manifests is not relevant.

Similar to the DPA, after matching one part of the key, the same method can be used to discover the remaining key parts.

### 3.1.4 Template Attacks

A much different family of Power Analysis attacks are the Template Attacks, introduced by Chari, Rao, and Rohatgi [21] in 2003. These attacks are very strong in an information theoretic sense, because

all the information leaking is potentially used. They usually require much less samples than correlation attacks. In order to create the templates for the attack, the attacker needs to have an exact copy of the targeted device to create a model of the its noise leakage. This is effortlessly achieved when the device in question is mass-produced and easily accessible. A typical template attack is then composed of two phases:

- 1. **Profiling Phase (or Training Phase)**. The attacker uses his replica of the targeted device to model the leakage regarding different operations.

- 2. Attack Phase. The power traces acquired for the targeted device are processed and compared with the model constructed in the first phase to obtain the secret key.

#### **Profiling Phase**

It is customary in signal processing to model a sample as a combination of a value and noise. This noise is best modelled as a random sample drawn from a noise probability distribution. In this phase, the goal is to develop a Multivariate Gaussian Model for the noise (power consumption) associated with different operations as accurately as possible.

To start, a large number of power traces are gathered using the clone system which is under full control of the attacking party. This way, this number is limited only by the time and available storage. The traces correspond to the power consumption of the device while performing the operation being modeled. While this can be used to distinguish any type of operation, the idea in template attacks is to consider each operation as performing an encryption with some different bits, depending on the key and plaintext. For example, reminding the selection function used also in DPA, one can consider the output of the AES S-Boxes to differentiate between operations. This way, it can be considered K = 256 different operations, where operation  $O_j$  is defined as encrypting a plaintext byte  $Pt_x$  and respective key part  $k^*$  such that  $S(Pt_x \oplus k^*) = j$ , with S being the S-Box substitution. The set of power traces acquired while performing  $O_j$  is represented by  $S_j$ . It is common practise to choose the plaintexts and keys randomly and mapping the corresponding trace to the correct set.

Modeling an entire power trace  $t_i$  with W samples,  $t_i[1], ..., t_i[W]$ , requires a W-dimension distribution, which proves unfeasible with a realistic value for Wa, in the order of thousands. This way, and because most points of the power trace are not relevant since they are not directly affected by the key, a group of N Points of Interest (PoIs) representing the critical and key-dependent moments of the trace are selected. Various techniques are used to select pick those points, as well as other methods to compress the data, as discussed later.

Having chosen N Pols,  $P_1, ..., P_N$ , the power traces can be transformed by keeping only the positions related to those points.

$$t = t[1], \dots t[W] \in \mathbb{R}^W \quad \mapsto \quad \dot{t} = t[P_1], \dots t[P_N] \in \mathbb{R}^N$$

(3.4)

Finally, the template parameters can be computed. These are the average,  $\mu_k \in \mathbb{R}^N$  and the covariance matrix  $\Sigma_k \in \mathbb{R}^{N \times N}$  defined as

$$\mu_k = \frac{1}{|S_k|} \sum_{i \in S_k} \dot{t}, \quad \Sigma_k = \frac{1}{|S_k| - 1} \sum_{i \in S_k} (\dot{t} - \mu_k) (\dot{t} - \mu_k)'$$

(3.5)

The template of the operation k is defined by the tuple  $(\mu_k, \Sigma_k)$ .

#### Points of Interest Selection and Data-Compressing Techniques

Different techniques exist in order to reduce the templates to a reasonable size. In fact, using the information of all the samples would waste a lot of computing time and power since most of them don't have any relevant information to the attack. It is then necessary to select that relevant Pols. Identifying those points leads not only to a serious reducing in data size, but also leads to discovering which operations of the algorithm under attack leak the most.

The original method, introduced in Chari et al. [21], consists of computing the sum of the pairwise differences between the average signal of each template,  $\Delta$ , and select only the *N* points at which large differences show up. In [22] an improvement is made by squaring the sums. This avoids hiding important peaks due to different signals, resulting in

$$\Delta = \sum_{u=1,v=1}^{K} (\mu_u - \mu_v)^2, \quad u \ge v.$$

(3.6)

with the resulting peaks of  $\Delta$  identifying the points at which the biggest differences show up. Since the sampling rate is usually higher than the clock frequency, it is normal that  $\Delta$  shows clusters of high points corresponding to the same operation of the cipher. This way, a usual method to contour this limitation is imposing a certain spacing between each chosen Pol.

In a more advanced method is also proposed, involving the T-Test to successfully detect the PoIs with noisy signals [22]. The T-Test is a statistical hypothesis test that distinguishes two data sets (i, j), which essentially compares the distance of the corresponding means  $(m_i, m_j)$  and their variability  $(\sigma_i^2, \sigma_j^2)$ . Among various implementations, depending on the similarity of the variances and sample sizes  $(n_i, n_j)$ of the data sets, the Welch's T-Test is given by

$$t_{value} = \frac{m_i - m_j}{\sqrt{\frac{\sigma_i^2}{n_i} + \frac{\sigma_j^2}{n_j}}}$$

(3.7)

and is used when the different sample sizes and variances are a possibility. This way, the Pols can be detected with

$$\Delta = \sum_{u=1,v=1}^{K} \left( \frac{m_u - m_v}{\sqrt{\frac{\sigma_u^2}{n_u} + \frac{\sigma_v^2}{n_v}}} \right)^2, \quad u \ge v$$

(3.8)

In order to reduce the data size in another way, Elaabid et al. [23] exploited the fact that the power dissipation in a CPU can be proportionally approximated by the Hamming weight of the computed data, in order to reduce the number of templates required. Therefore, it is possible to model a sensitive part of the algorithm and create a template for each possible Hamming Weight of a state of that model. In

AES, the diffusion of the S-Box makes it a good part to model. With a key part of 8 bits, this technique uses 9 templates instead of  $2^8 = 256$ . Despite this only allowing the discovery of the Hamming weight of the key part, its exact value can be recovered by repeating the attack with other plaintexts.

### **Attack Phase**

Having computed the templates  $(\mu_k, \Sigma_k)$ , it is necessary to establish how to discover the subkey  $\hat{k}$  which resulted in the set of traces,  $\hat{S}$ , acquired in the targeted machine. Recalling that the leaking noise is approximately modeled by a multivariate normal distribution, the probability distribution of the noise occurring from operation  $O_k$  is given by the N-dimensional normal distribution  $p_k(.)$  where the probability of observing a noise vector z is

$$p_k(z) = \frac{1}{(2\pi)^N |\Sigma_k|} exp\left(-\frac{1}{2}z'\Sigma_k^{-1}z\right), \quad z \in \mathbb{R}^N$$

(3.9)

with  $|\Sigma_k|$  representing the determinant of  $\Sigma_k$ , and  $\Sigma_k^{-1}$  its inverse.

This way, to classify a power trace  $\hat{t}$  from the set  $\hat{S}$  a maximum likelihood hypothesis test is performed. For each  $k \in [0, K[$ , the noise in  $\hat{t}$  is extracted at the N Pols, yielding a noise vector  $n_k(\hat{t})$  with

$$n_k(\hat{t}) = t[P_1] - \mu_k[P_1], \dots, t[P_N] - \mu_k[P_1] \in \mathbb{R}^N.$$

(3.10)

Then, the probability to observe such a noise vector can be computed using Equation (3.9). Consequentially, the hypothesis k that maximises that probability is the best candidate for the observed trace  $\hat{t}$ . When more than one trace is available, the probability to be maxed is found with,

$$P_k = \prod_{\hat{t} \in \hat{S}} p_k(n_k(\hat{t})). \tag{3.11}$$

Other ways to correctly identify the template exist. For instance, [24] uses Support Vector Machines, a family of machine learning algorithms, to tackle this challenge. After acquiring one byte of the key, the power traces can be mapped to new sets according to the next key and plaintext bytes, and the process is repeated.

### 3.1.5 Countermeasures and Counter-countermeasures

Given the importance of these kind of attacks, a great effort has been made in order to find countermeasures to prevent them [25]. Different categorisations can be done on this countermeasures, that ultimately divide them into Software-based / High-level versus Hardware-based / Low-level [20]. In [26] a Medium-level, as something between the two extremes, is also presented.